운영체제와 하드웨어 간의 상호동작(폴링)

운영체제는 레지스터(상태, 명령, 데이터 레지스터)를 읽고 쓰는 것을 통해 하드웨어 장치의 동작을 제어할 수 있게 된다.

- 상태(Status) : 하드웨어 장치의 현재 상태를 읽을 수 있는 레지스터

- 명령(Command) : 하드웨어 장치가 특정 동작을 하도록 요청할 때 사용

- 데이터(Data) : 하드웨어 장치에 데이터를 보내거나 받거나 할 때 사용

운영체제와 하드웨어 장치 간에 폴링을 통한 상호작용은 다음과 같다.

- 폴링(Polling)을 한다.

- 폴링(Polling) : 운영체제가 하드웨어 장치의 상태 레지스터를 읽음으로써 명령의 수신 여부를 주기적으로 확인하는 것이다.

- 즉, 하드웨어장치의 상태를 수시로 체크하여 명령을 받을 수 있는지 확인하는 것을 말한다.

- 운영체제가 데이터 레지스터에 데이터를 전달한다.

- 운영체제가 명령 레지스터에 명령을 기록한다.

- 운영체제는 하드웨어 장치가 특정 동작을 처리하였는지 폴링 반복문을 돌면서 기다린다.(성공/실패 코드를 받게 됨)

폴링을 하는 동안에는 다른 프로세스에게 CPU를 양도하지 않고 하드웨어 장치가 동작을 완료할 때까지 계속 루프를 돌면서 하드웨어 상태를 체크하게 된다.

→ 하드웨어 장치의 속도는 매우 느리기 때문에 CPU를 많이 낭비하게 된다.

인터럽트

CPU가 프로그램을 실행하고 있을 때, I/O 하드웨어 등의 장치에 예외상황이 발생하여 처리가 필요할 경우 CPU에게 알려 처리할 수 있도록 하는 것을 말한다.

- CPU의 정상적인 프로그램 실행을 방해했다는 의미

운영체제는 디바이스를 폴링하는 대신에 I/O 요청한 프로세스를 블록시키고 CPU를 다른 프로세스에게 양도한다. 장치가 끝마치면 하드웨어 인터럽트를 발생시키고 CPU는 운영체제가 미리 정의해 놓은 인터럽트 서비스 루틴(ISR) 또는 인터럽트 핸들러(Interrput Handler)를 실행한다. 인터럽트 핸들러는 입출력 요청, I/O 대기중인 프로세스 깨우기 등을 하여 프로세스가 작업을 계속할 수 있도록 한다.

외부 인터럽트, 내부 인터럽트, 소프트웨어 인터럽트가 있다.

- 외부/내부 인터럽트는 CPU의 하드웨어 신호에 의해 발생

- 소프트웨어 인터럽트는 명령어의 수행에 의해 발생

외부 인터럽트

입출력 장치, 타이밍 장치, 전원 등 외부적인 요인으로 발생

- 타이머 인터럽트 : 타이머가 일정한 시간 간격으로 중앙처리장치에게 인터럽트를 요청

- 입출력 인터럽트 : 속도가 느린 입출력장치가 입출력 준비가 완료되었음을 알리기 위해 인터럽트를 요청

내부 인터럽트

Trap이라고 부르며, 잘못된 명령이나 데이터를 사용할 때 발생

0으로 나누기, 오버플로우, 명령어 잘못 사용한 경우(Exception)

- 하드웨어 고장(Hardware Interrupt)

- 컴퓨터 고장

- 데이터 전달 과정에서의 비트 오류

- 전원이 나간 경우

- 실행할 수 없는 명령어 : 기억장치에서 인출한 명령어의 비트 패턴이 정의되어 있지 않은 경우

- 명령어 실행 오류 : 나누기 0을 하는 경우

- 사용 권한 위배 : 사용자가 운영체제만 사용할 수 있는 자원에 액세스하는 경우

소프트웨어 인터럽트

프로그램 처리 중 명령의 요청에 의해 발생한 것(SVC 인터럽트)

- 사용자가 프로그램을 실행시킬 때 발생 : 소프트웨어 이용 중에 다른 프로세스를 실행시키면 시분할 처리를 위해 자원 할당 동작이 수행된다.

인터럽트 처리 과정

우선, 명령어 사이클은 인출(fetch stage)과 실행(execution stage) 두 가지 단계를 반복해서 수행한다.

그런데 인터럽트 요청이 들어왔다고 해서 바로 이를 처리하는 것이 아니라, 명령어 N의 실행 단계를 마쳐야 한다. 명령어의 실행단계를 마칠 때마다 중앙처리장치(CPU)는 반복적으로 인터럽트 요청이 있는지 계속해서 확인한다. 인터럽트 요청이 있어야 인터럽트 서비스 단계를 진행한다.

좀 더 큰 개념으로 살펴본다면 아래와 같은 그림이 된다.

주 프로그램이 실행되다가 인터럽트가 발생했다. 현재 수행 중인 프로그램을 멈추고, 상태 레지스터와 PC 등을 스택에 잠시 저장한 뒤에 인터럽트 서비스 루틴으로 간다. (잠시 저장하는 이유는, 인터럽트 서비스 루틴이 끝난 뒤 다시 원래 작업으로 돌아와야 하기 때문)

process A 실행 중 디스크에서 어떤 데이터를 읽어오라는 명령을 받았다고 가정해보자.

- process A는 system call을 통해 인터럽트를 발생시킨다.

- CPU는 현재 진행 중인 기계어 코드를 완료한다.

- 현재까지 수행중이었던 상태를 해당 process의 PCB(Process Control Block)에 저장한다. (수행중이던 MEMORY주소, 레지스터 값, 하드웨어 상태 등...)

- PC(Program Counter, IP)에 다음에 실행할 명령의 주소를 저장한다.

- 인터럽트 벡터를 읽고 ISR 주소값을 얻어 ISR(Interrupt Service Routine)로 점프하여 루틴을 실행한다.

- 해당 코드를 실행한다.

- 해당 일을 다 처리하면, 대피시킨 레지스터를 복원한다.

- ISR의 끝에 IRET 명령어에 의해 인터럽트가 해제 된다.

- IRET : Intel 아키텍처의 어셈블리 명령어 중 하나로 '인터럽트 처리 시에 모든 처리를 완료하고 다시 태스크로 복구'하는 명령어

- IRET 명령어가 실행되면, 대피시킨 PC 값을 복원하여 이전 실행 위치로 복원한다.

- 인터럽트 번호는 예외상황 인터럽트를 제외하고 운영체제가 결정한다. 리눅스에서 인터럽트 번호는 아래와 같다.

- 0 ~ 31 : 예외상황 인터럽트

- 32 ~ 47 : 하드웨어 인터럽트

- 128 : 시스템 콜

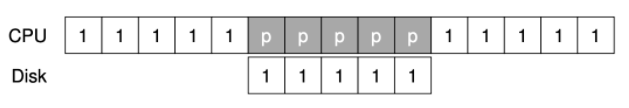

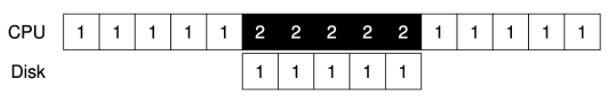

폴링 vs 인터럽트

- 폴링 : 프로세스 1이 실행 중에 Disk로부터 I/O 요청이 발생하면, 운영체제는 I/O 요청이 완료될때까지 반복적으로 폴링한다.(p). 디스크가 I/O 요청의 처리를 완료하면 프로세스 1이 다시 동작한다.

- 인터럽트 : 프로세스 1이 실행 중에 있다가 Disk로부터 I/O 요청을 받으면, 요청을 처리하는 동안에 운영체제는 프로세스 2를 CPU에서 실행시키게 된다. 프로세스 1에 대한 디스크 요청이 완료가 되면 인터럽트를 발생시켜 운영체제는 프로세스 1을 다시 CPU에서 실행시킨다.

이처럼 인터럽트를 사용하면 CPU 연산과 I/O 장치 작업을 중첩시켜 수행할 수 있게 된다. 그렇기 때문에 폴링보다 CPU 사용률을 높일 수 있다.

- 하지만 무조건 폴링보다 좋다고 할 수는 없다.

- 예를 들어, 단 한번의 폴링으로만 끝날 정도의 빠른 하드웨어 장치라면 인터럽트보다 폴링이 더 효율적이라고 할 수 있다.

- 인터럽트를 사용하게 되면 현재 실행중인 프로세스를 다른 프로세스로 문맥교환(Context Switching)하게 되고 이 때 많은 비용이 수반되기 때문이다.

- 그렇기 때문에 빠른 하드웨어 장치라면 폴링이 더 효율적이고 느린 하드웨어 장치라면 인터럽트가 더 효율적이라고 할 수 있다.

즉, 컨트롤러가 입력을 받아들이는 방법(우선순위 판별방법)에는 두가지가 있다.

- 폴링 방식

- 사용자가 명령어를 사용해 입력 핀의 값을 계속 읽어 변화를 알아내는 방식

- 인터럽트 요청 플래그를 차례로 비교하여 우선순위가 가장 높은 인터럽트 자원을 찾아 이에 맞는 인터럽트 서비스 루틴을 수행한다. (하드웨어에 비해 속도 느림)

- 인터럽트 방식

- MCU(마이크로 컨트롤러 유닛, Micro Controller Unit, 컴퓨터)자체가 하드웨어적으로 변화를 체크하여 변화 시에만 일정한 동작을 하는 방식

- Daisy Chain

- 병렬 우선순위 부여

- MCU(마이크로 컨트롤러 유닛, Micro Controller Unit, 컴퓨터)자체가 하드웨어적으로 변화를 체크하여 변화 시에만 일정한 동작을 하는 방식

인터럽트 방식은 하드웨어로 지원을 받아야 하는 제약이 있지만, 폴링에 비해 신속하게 대응하는 것이 가능하다. 따라서 실시간 대응이 필요할 때는 필수적인 기능이다.

즉, 인터럽트는 발생시기를 예측하기 힘든 경우에 컨트롤러가 가장 빠르게 대응할 수 있는 방법이다.

동기/비동기 관점에서 나눠본 인터럽트

인터럽트(interrupt), 예외(exception), 트랩(trap)의 비교 - Easy is Perfect

여러 가지 블로그를 찾아 보던 중에 좋은 자료가 있어서 간결하게 하여 포스팅하여 정리하였습니다. - 인터럽트 (인터럽트에는 비동기와 동기가 있다. 비동기는 interrupt, 동기는 exception) > Asynchron

melonicedlatte.com

참고

'📌CS > OS' 카테고리의 다른 글

| [OS] 시스템 호출(System Calls) (0) | 2021.08.31 |

|---|---|

| [OS] 프로세스 주소 공간 (0) | 2021.08.23 |

| [OS] 프로세스 vs 스레드 (0) | 2021.08.18 |

| [OS] CPU 스케줄링 (0) | 2021.08.11 |

| [OS] 스케줄러의 종류: 장기, 중기, 단기 스케줄러 (0) | 2021.08.04 |

댓글